RISC-V on Enzian

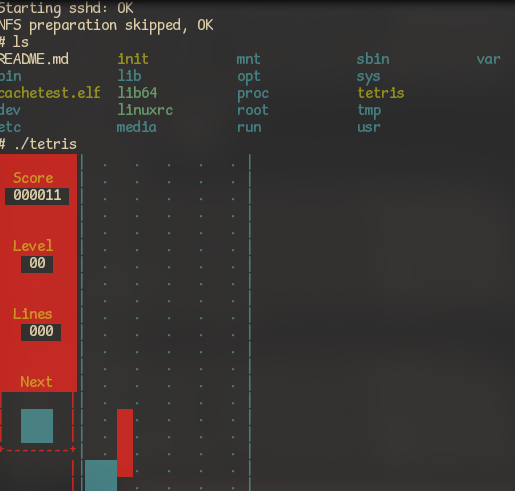

Thanks to the hard work of a bachelor’s student, Diego de los Santos, we have brought up the Rocket RISC-V core on the Enzian’s FPGA. We are able to load an image from the CPU side, across ECI, directly into the FPGA’s DRAM. We can then boot into Linux on the RISC-V core. While clock speed is obviously limited in the FPGA implementation (currently 100MHz) this is still many orders of magnitude faster than RTL simulation. This allows us to run more realistic, larger memory benchmarks on RISC-V. We can then examine power and performance implications of various microarchitectural changes.

A running RISC-V core opens up a number of future projects and research directions. Practically, we’re working to create a module to translate ECI messages to Tilelink to communicate between the two heterogeneous cores. Eventually this could include a shared coherence domain. We also will begin to attach perhipherals beyond DRAM (e.g. NVMe and networking). In the long term, we can use this as a platform to explore multi-architectural, heterogeneous operating systems.

If you’re interested in research in this area, please get in touch.